Programmering av IC kretsar - VHDL

Godkväll!

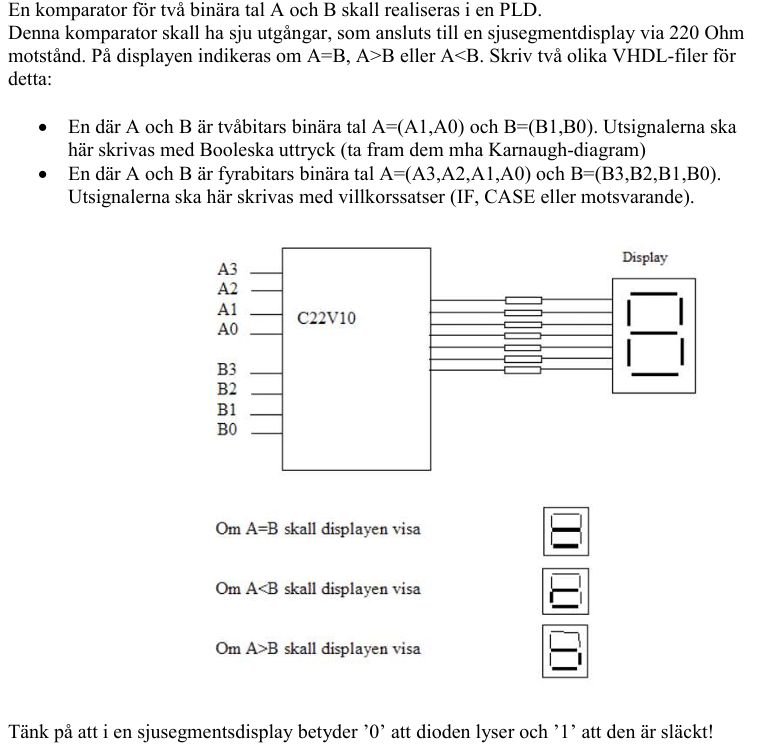

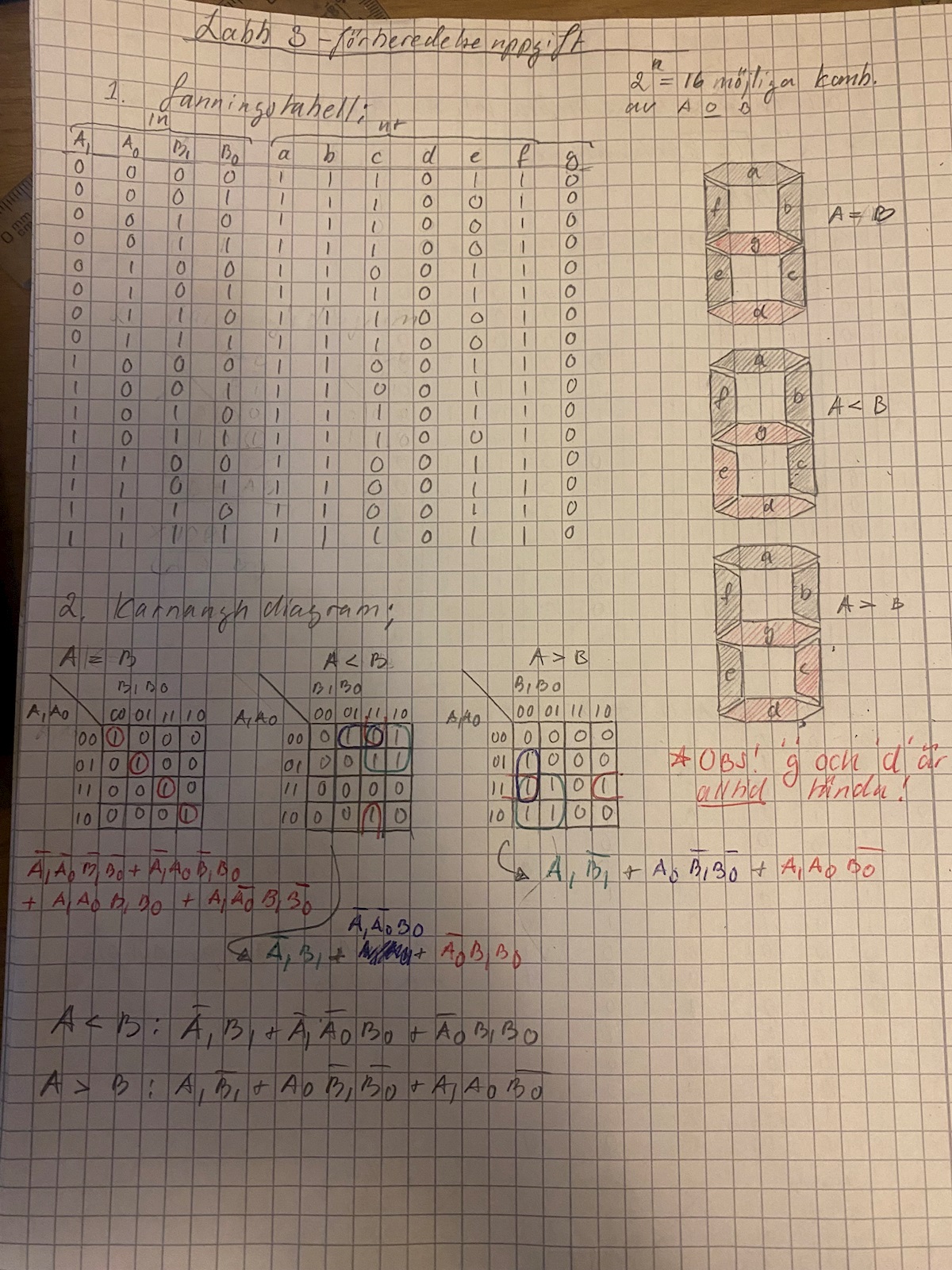

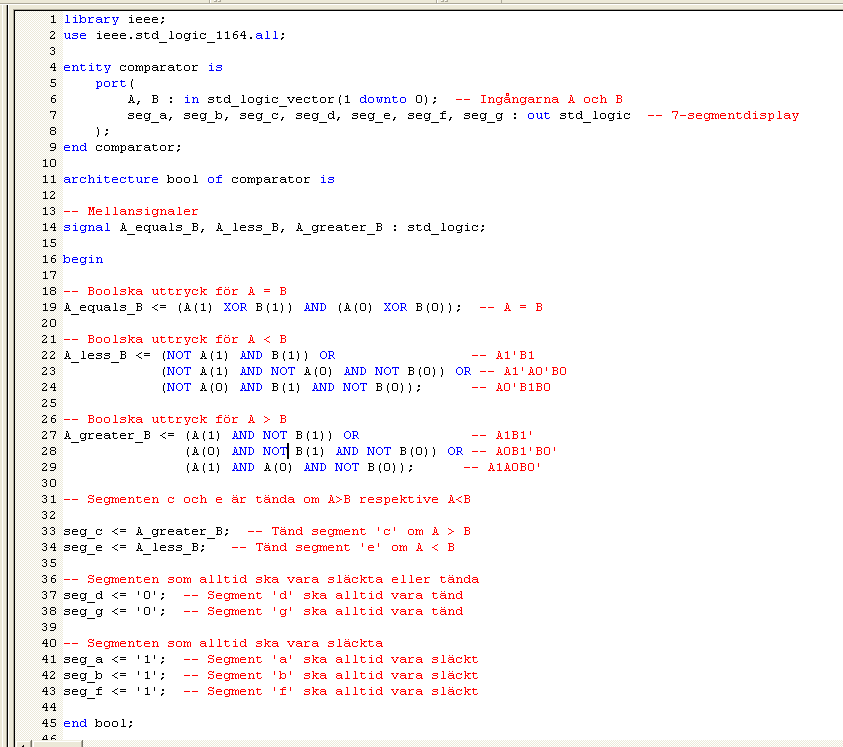

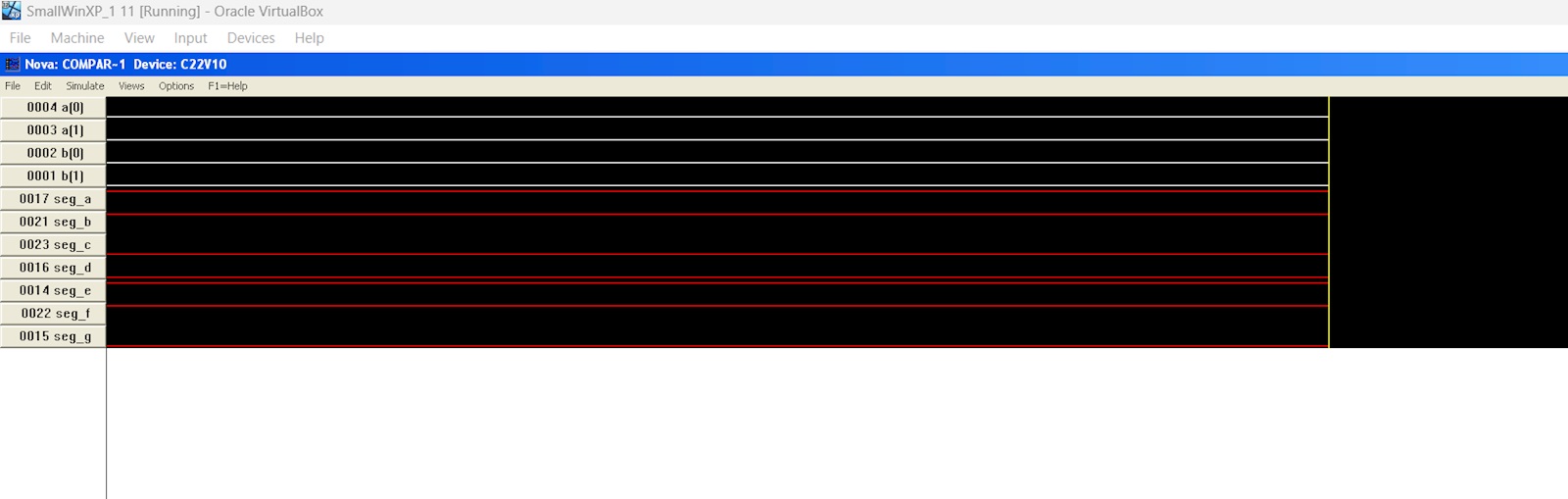

Jag har kört fast på en uppgift där man ska programera en IC-krets med VHDL. Då jag verkligen försökt med alla medel anser jag att det är klokast att bara publciera en bild på uppgiften, mina sanningstabeller, karnaughdiagram och givevis också koden jag skrivit. precis som beskrivningen säger handlar det om att man ska skicka in två signlaer till en komparator, en där A och B är tvåbitars binära tal A=(A1,A0) och B=(B1,B0). Vi använder en gammal virtuella maskin som fått ladda ner med utvecklingsmiljön galaxy och simulatorn nova ingår. Som synes räcker det med att bara kolla på simulationen för att konstatera att något gått snett eftersom segment c lyser trots att A=B.

utsignalerna ska alltså skrivas med boolska uttryck och i det första fallet inte med CASE, If sats. (Jag lyckades skriva kod där utsignalerna beter sig rätt där jag tilldelade värdet '1' resp. '0' till segmenten. Men uppgiften kräver alltså att det ska realiserar endast med boolska uttryck.).

* Jag är givevis helt nybörjare på VHDL och hoppas verklgien att det finns någon som här som är bekant med det :)

Trevlig kväll och fortsatt trevlig helg för övrigt :)

Teroin (OBS! jag vet att det råder negativ logik - kanske där det slår snett någonstans?)

VHDL kod

Simulering (OBS! Som synes lyser segment c (aktivt låg) så någonstans fallerar min logik...)

Väldigt sent svar det här, hoppas det inte är försent.

Vad jag förstår så ska dina mellansignaler bli etta om villkoren är uppfyllda, t.ex. A_equals_B = 1 om A=B.

A_equals_B:

XOR blir väl ett om bitarna är olika, inte lika. T.ex. A(1) XOR B(1) = 0 XOR 1 = 1. Eller?

A_less_B:

I andra och tredje raden står NOT B(0). Ska väl vara bara B(0)?

Segment c och e är inte definierade om A = B. Risk att utgångarna för dessa hamnar i ett defaultläge.

En liten fråga om din simulering. Det ser ut som du har konstant 0000 på ingångarna.

Kan du ta med mellansignalerna här också så blir det kanske lite lättare att felsöka.

ThomasN skrev:Väldigt sent svar det här, hoppas det inte är försent.

Vad jag förstår så ska dina mellansignaler bli etta om villkoren är uppfyllda, t.ex. A_equals_B = 1 om A=B.

A_equals_B:

XOR blir väl ett om bitarna är olika, inte lika. T.ex. A(1) XOR B(1) = 0 XOR 1 = 1. Eller?A_less_B:

I andra och tredje raden står NOT B(0). Ska väl vara bara B(0)?Segment c och e är inte definierade om A = B. Risk att utgångarna för dessa hamnar i ett defaultläge.

En liten fråga om din simulering. Det ser ut som du har konstant 0000 på ingångarna.

Kan du ta med mellansignalerna här också så blir det kanske lite lättare att felsöka.

Varmt tack för svar! Och nej, det är inte för sent :)

Det stämmer beträffande ditt resonemang men XOR men det slog mig att logiken för A=B inte behövs eftersom dessa segment ändå alltid kommer att lysa (segment d och g). Det är därför som jag ändå har tilldelat dem värdet 0 längre ner i koden så de ska inte påverkas. Nu har jag tyvärr inte datorn till hands just nu men menar du att mina bilskatter uttryck härleds ur karnaugh diagrammen inte stämmer eller att de inte stämmer överens med koden? Det kan mycket väl vara så att jag skrivit fel logik i med VHDL, ser nu att det mycket riktigt är som du säger iallafall beträffande att not(B(0)) respektive B(0). Och det stämmer också att jag har 0000 som i signaler men det borde ju också innebära att endast segment d och g är tända dvd har låg nivå, 0, då A = B. Som du säkert redan sätt lyser även segment c i detta läge, vilket alltså är fel.

Så vitt jag kan se stämmer ekvationerna som du fått ut ur Karnaughdigrammen, men det står inte detsamma i VHDL-koden (det är vad jag menar med att det ska vara B(0) och inte NOT B(0) på två ställen).

Jag håller med om att logiken för A=B inte behövs.

Jag får också ta tillbaka mitt påstående att segment c och e inte är definierade när A=B. Det är de visst!

Det är väl så att A_less_B blir '1' om A<B och A_greater_B blir '1' om A>B? Om så är fallet så borde det väl bli styrningen av utgångarna bli:

seg_c = NOT( A_greater_B)

seg_e = NOT(A_less_B)

ThomasN skrev:Så vitt jag kan se stämmer ekvationerna som du fått ut ur Karnaughdigrammen, men det står inte detsamma i VHDL-koden (det är vad jag menar med att det ska vara B(0) och inte NOT B(0) på två ställen).

Jag håller med om att logiken för A=B inte behövs.

Jag får också ta tillbaka mitt påstående att segment c och e inte är definierade när A=B. Det är de visst!Det är väl så att A_less_B blir '1' om A<B och A_greater_B blir '1' om A>B? Om så är fallet så borde det väl bli styrningen av utgångarna bli:

seg_c = NOT( A_greater_B)

seg_e = NOT(A_less_B)

Dåså, intitialt, ursäkta en massa stavfel i mitt förra meddelande. (Jag och autocorrect är inte alltid vänner...). Jag ändrade koden precis enligt ditt påpekande och det gav resultat. dock gjorde den det omvända. MEN, det jag märkte var att signalerna beter sig helt korrekt (iallafall vad jag kan se...) om jag inverterade båda uttrycken flr segment c och e. (Varför detta sker är jag lite för trött för att lista ut just nu men uppenbarligen verkar det funka. Givetvis kan mina trötta ögon svika mig och då är det bara att påpeka detta så fortsätter jag mitt felsökande :)

Ny kod (OBS! A>B och A<B är ändrade enligt dina instruktioner, men signalerna är också inverterade)

Utsignaler vid 0000

A>B

Archie skrev:ThomasN skrev:Så vitt jag kan se stämmer ekvationerna som du fått ut ur Karnaughdigrammen, men det står inte detsamma i VHDL-koden (det är vad jag menar med att det ska vara B(0) och inte NOT B(0) på två ställen).

Jag håller med om att logiken för A=B inte behövs.

Jag får också ta tillbaka mitt påstående att segment c och e inte är definierade när A=B. Det är de visst!Det är väl så att A_less_B blir '1' om A<B och A_greater_B blir '1' om A>B? Om så är fallet så borde det väl bli styrningen av utgångarna bli:

seg_c = NOT( A_greater_B)

seg_e = NOT(A_less_B)Dåså, intitialt, ursäkta en massa stavfel i mitt förra meddelande. (Jag och autocorrect är inte alltid vänner...). Jag ändrade koden precis enligt ditt påpekande och det gav resultat. dock gjorde den det omvända. MEN, det jag märkte var att signalerna beter sig helt korrekt (iallafall vad jag kan se...) om jag inverterade båda uttrycken flr segment c och e. (Varför detta sker är jag lite för trött för att lista ut just nu men uppenbarligen verkar det funka. Givetvis kan mina trötta ögon svika mig och då är det bara att påpeka detta så fortsätter jag mitt felsökande :)

Ny kod (OBS! A>B och A<B är ändrade enligt dina instruktioner, men signalerna är också inverterade)

Utsignaler vid 0000

A>B

Varierande signaler

Verkar fungera nu, eller?

ThomasN skrev:Verkar fungera nu, eller?

Ja, iallafall utifrån vad jag kan se av simuleringen. Varmt tack för hjälpen!