Ingångs-/utgångsresistans

|

|

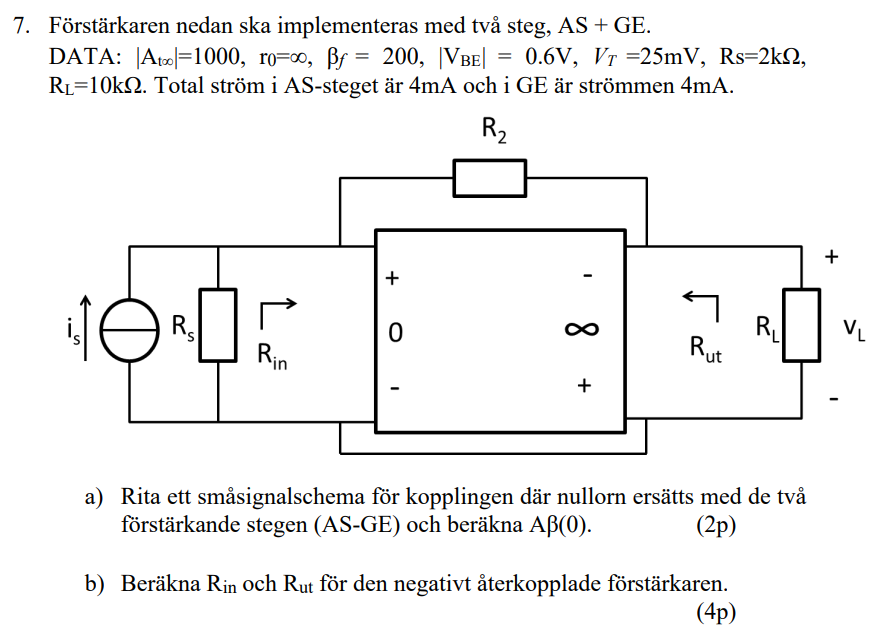

Hej, kan någon hjälpa mig att förstå hur man beräknar ingångs och utgångsresistans?

Det gäller att .

På samma sätt .

Har också för mig att man måste nollställa ut-/insignal när man beräknar detta, men vet inte hur.

Hur kan man göra beräkningarna zi och zo för förstärkaren till höger?

Är en hel del jag inte förstår här, hoppas jag kan bidra lite i alla fall.

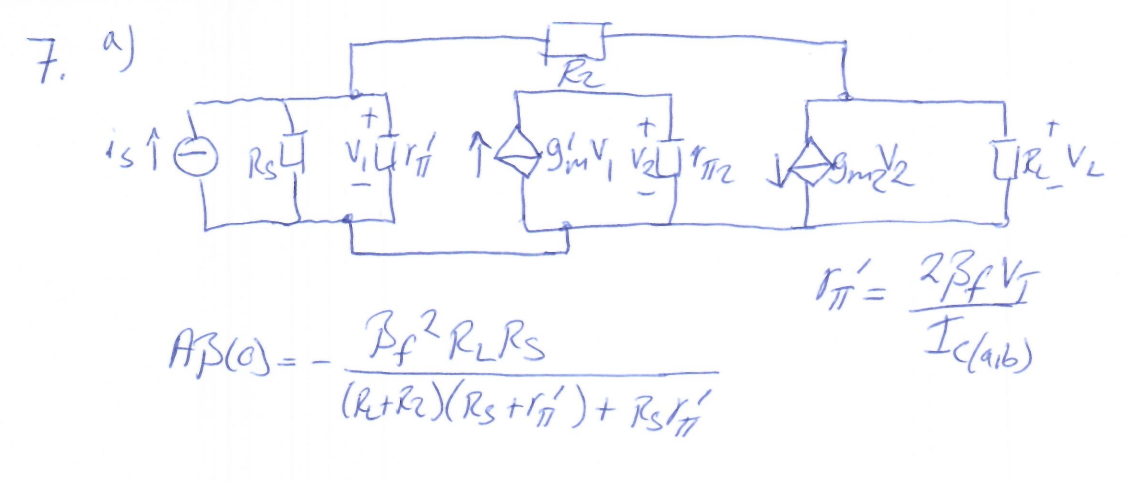

Jag antar att första steget är en FET-transistor (AS-steg?) och andra steget ett GE-steg med en bipolär transistor. I småsignalschemat ser det ut som det är två FET-steg.

Vad är zi ? Är det inimpedansen i det första steget (utan återkoppling)?

FET-transistor (AS-steg?)

Ja det är ett AS steg, men BJT.

Vad är zi ?

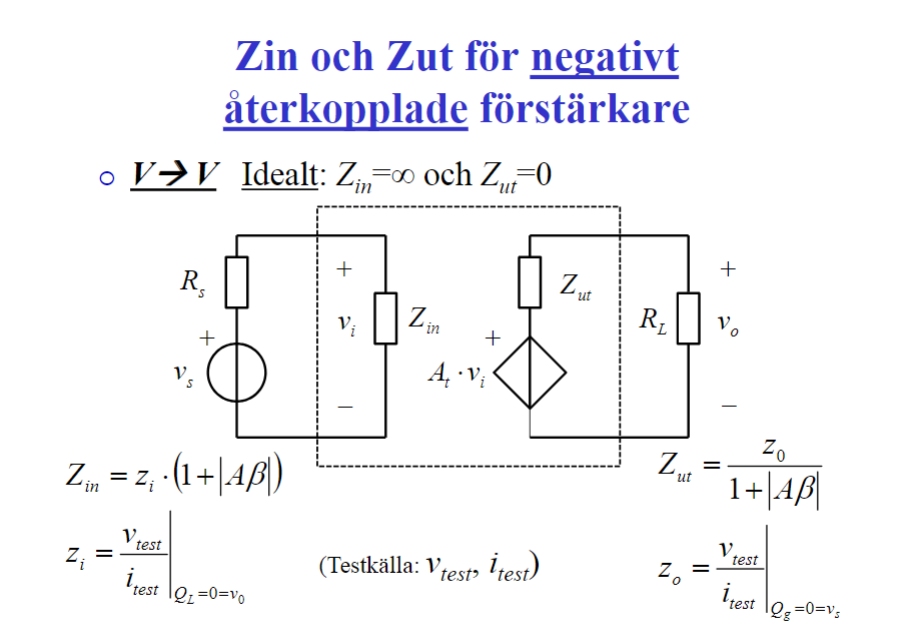

Det är ingångsimpedansen. Sen Z_in (stort Z) är ingångsimpedansen efter kompensering, som blir mer ideal med faktorn (1 + AB).

Det är z_in jag behöver räkna ut, samt z_o (små z).

Tror jag har löst z_in iaf. När VL= så är R2 parallell med rpi' och zin = R2 || r'_pi. Fortfarande lite osäker på varför R_s inte räknas med, men antar att den försvinner när man tar bort i_s och tillsätter en testkälla i_t.

Sen tycker jag att r_o är lite trixigare.

Har fortfarande svårt att se kopplingen. Är båda stegen uppbyggda med bipolära transistorer? I småsignalmodellen ser det ut att vara två FET.

Har du ritat ett "riktigt" schema?

ThomasN skrev:Har fortfarande svårt att se kopplingen. Är båda stegen uppbyggda med bipolära transistorer? I småsignalmodellen ser det ut att vara två FET.

Har du ritat ett "riktigt" schema?

Detta är modellen för AS-steget som vi använder. Kapacitanserna är avbrott i detta fallet. Utgångsterminalerna är korsade för att upprätthålla den negativa överföringen (annars skulle det bli negativ (AS) plus negativ (GE) = positiv). Det är därför strömkällan pekar uppåt istället. Lägg också märke till att AS steget inte är kortslutet i emittern (något som bland annat utnyttjas för att inte kortsluta överföringsnätet i en V-V eller I-I förstärkare). Kanske är det det som påminner om en MOSFET, där det är avbrott mellan gate och source?

Detta är modellen för AS-steget som vi använder. Kapacitanserna är avbrott i detta fallet. Utgångsterminalerna är korsade för att upprätthålla den negativa överföringen (annars skulle det bli negativ (AS) plus negativ (GE) = positiv). Det är därför strömkällan pekar uppåt istället. Lägg också märke till att AS steget inte är kortslutet i emittern (något som bland annat utnyttjas för att inte kortsluta överföringsnätet i en V-V eller I-I förstärkare). Kanske är det det som påminner om en MOSFET, där det är avbrott mellan gate och source?

GE steget har en snarlik modell, fast med kortsluten emitter och andra småsignalparametrar.

Den modellen är jag inte speciellt bekant med, tyvärr. Känns som jag kommer med mer frågor än svar.

En liten fråga till bara: Är inte zi samma sak som ?

(Om man tittar på figuren i uppgiften så ser det ut som Zin gäller för förstärkaren, oberoende av Rs)

Detta är i princip den enda jag har att gå på. Du ser där att zi och z0 beräknas med med särskilda villkor, att in/utsignal ska nollställas. Jag förstår inte riktigt varför heller.

Wikipedia hade en del beskrivningar om Hybrid-Pi:

https://en.wikipedia.org/wiki/Hybrid-pi_model

Där finns bl.a en formel för att räkna ut . Är det samma som zi?

Impedanserna ska nog räknas när förstärkaren inte finns signalspänningar på un eller utgång, men DC-spänningar/strömmar som sätts av arbetspunkten finns ju där. T.ex de 4mA i varje steg.

Det här är mest gissningar, jag känner att jag kan för lite om detta.

ThomasN skrev:Där finns bl.a en formel för att räkna ut . Är det samma som zi?

Tror inte de är samma. I facit blev zi = r’pi || RL. Detta i och med att när VL är 0 så sitter RL parallellt med ingången.

Impedanserna ska nog beräknas när förstärkaren inte finns signalspänningar på un eller utgång,

Det där låter ganska rimligt faktiskt.

Aja, nu är tentan redan skriven (och det kom inte ens någon fråga om detta) så det är ingen panik om jag inte förstår detta i nuläget. Någon gång i framtiden kanske det klarnar för mig. Tack för all hjälp!